Cadence Clarity 2020是一款专业的CAD设计软件。CAD设计师都在使用的CAD设计软件Cadence Clarity 2020。它主要用于PCB和IC封装结构的3D电磁场解决方案领域,可以满足该行业的所有用户;该程序提供批量PCB设计和制造所需的DFM可制造性设计解决方案,并且该程序支持PCB网络。分析,支持PCB可测试性分析,支持PCB裸板分析;不仅如此,该工具还支持PCB组装分析和PCB可靠性分析等,分析规则可以根据用户需求自定义定义;面对设计复杂性和专业分工的增加,项目团队和远程分布式办公室迫切需要进行人与人的协作分工。通过此过程,可以同时切割并移交PCB设计。多人协作和分工可缩短设计时间并提高效率。另外,它还支持HDI高密度设计,可以切割分层的设计以适应小型化设计应用;需要它的用户可以下载体验。

破解方法:

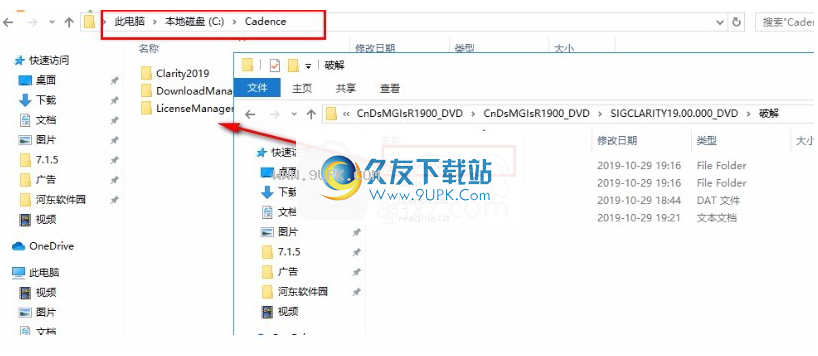

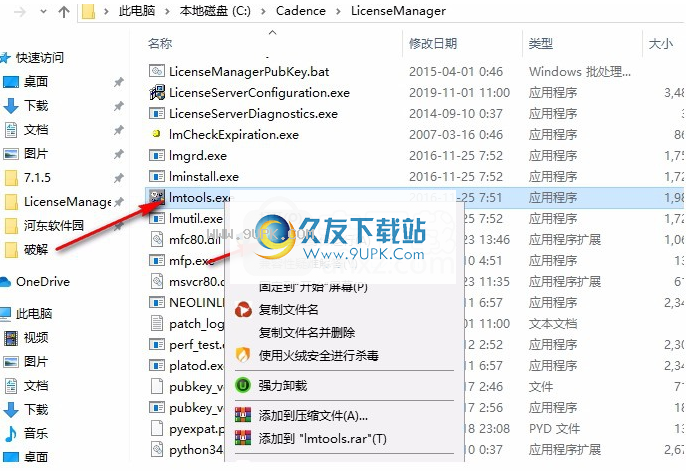

1.程序安装完成后,请勿先运行程序,打开安装包,然后将文件夹中的破解文件LicenseManager复制到C:\ Cadence进行替换

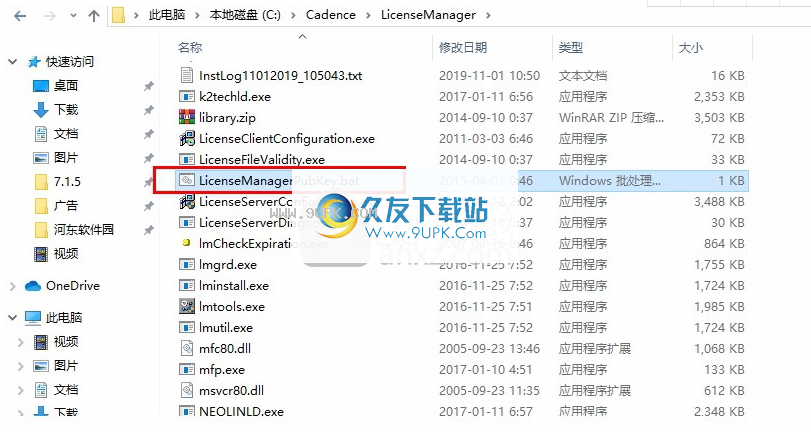

2.替换后打开LicenseManager文件夹,双击以启动LicenseManagerPubKey.bat,然后等待操作结束

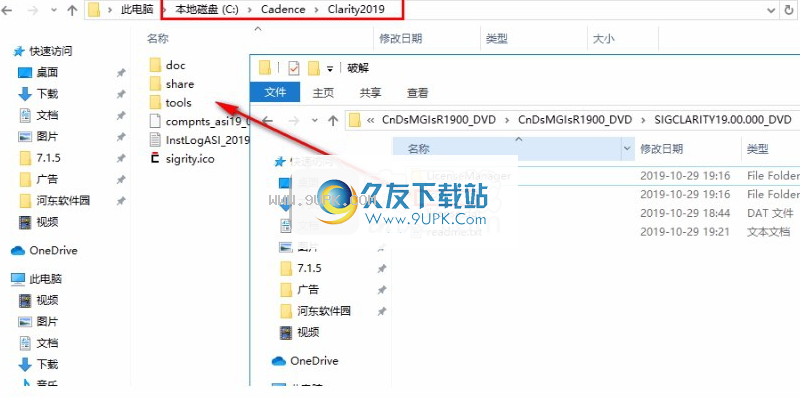

3,继续将破解文件夹中的工具复制到C:\ Cadence \ Clarity2019并替换

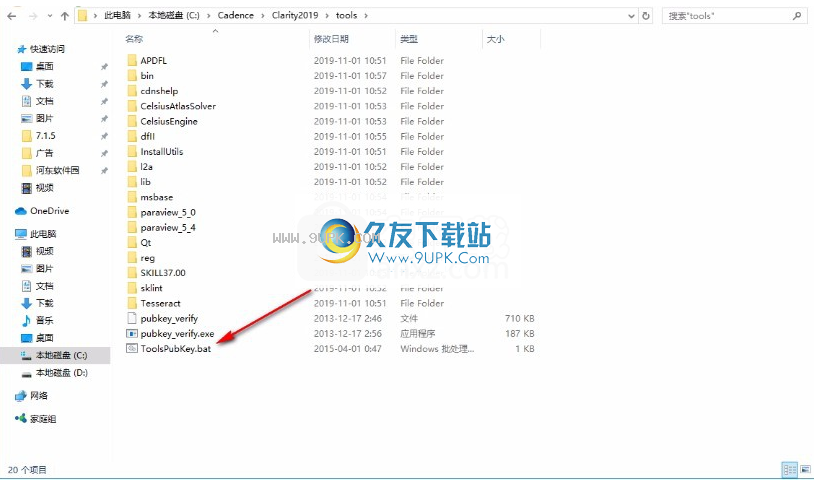

4.更换后,打开工具文件夹,运行ToolsPubKey.bat,等待几秒钟以开始加载数据,直到界面自动关闭

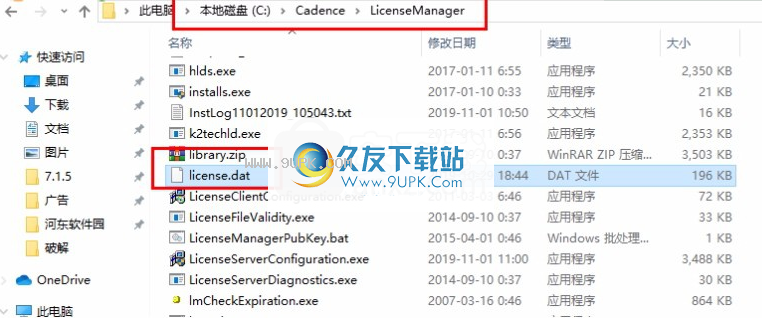

5.将破解文件夹中的license.dat复制到C:\ Cadence \ LicenseManager

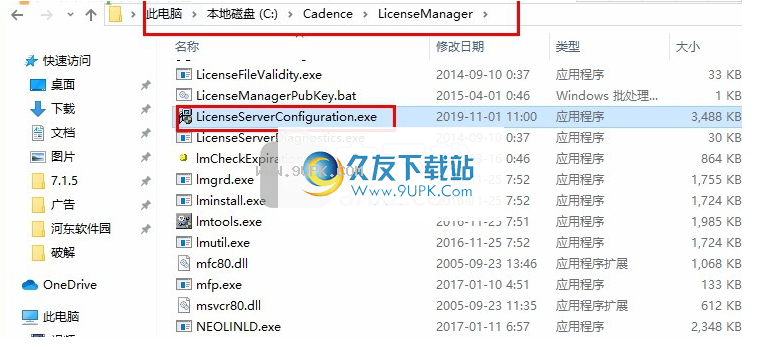

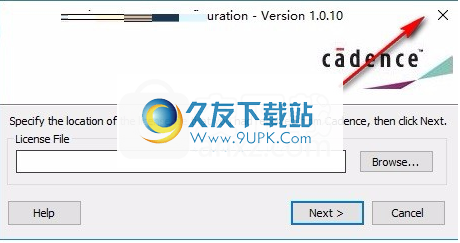

6,然后在“管理员”中打开LicenseServerConfiguration.exe配置许可证文件

7.添加许可证,地址为C:\ Cadence \ LicenseManager \ license.dat,单击下一步。

8.在此处进入界面,直接单击下一步,然后等待软件识别许可证内容

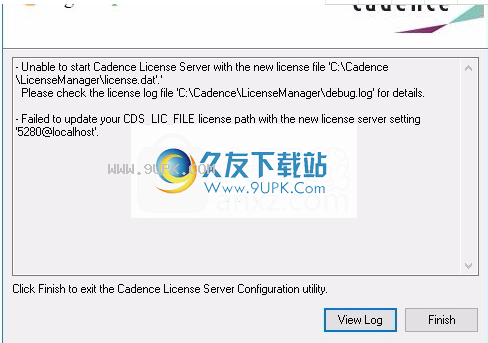

9.进入以下界面后,您可以直接单击完成按钮,然后可以继续进行下一步。

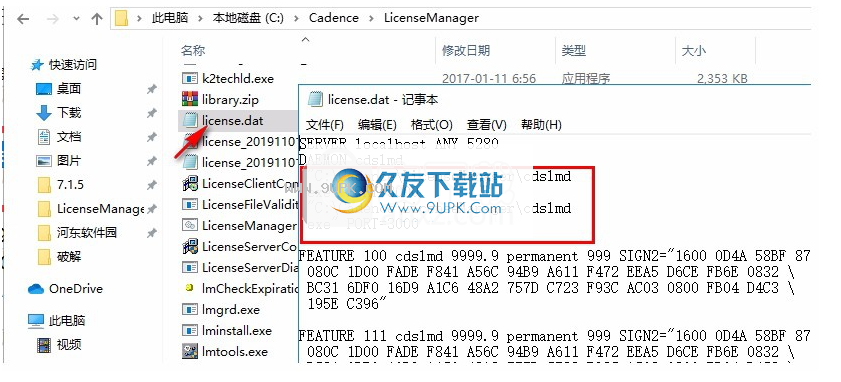

10.在记事本中打开license.dat,删除下图中的所有内容,然后保存license.dat

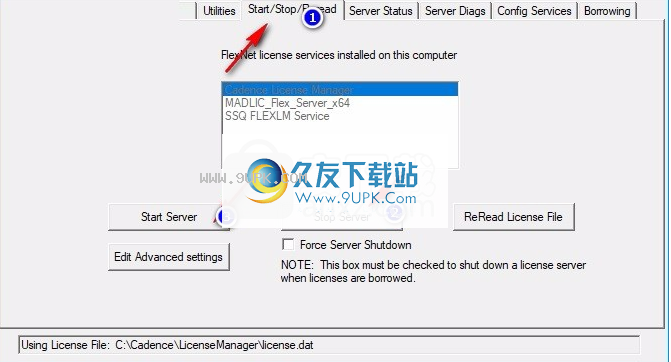

11.右键单击管理员以运行lmtools.exe并切换到“开始/停止/重新读取”

12.用户可以按照图中的标签进行操作,单击“停止服务器”以停止服务,然后单击“启动服务器”以启动服务。

软件特色:

LarClarity 3D Workbench提供了四个主要的应用程序流程:

导入从SPD导入-请勿执行或仅做少量修改,分析和查看结果。

从SPD导入-使用本机3D零件和操作来扩展,分析和查看结果。

通过3D实体模型导入从SPD-Enhance导入,通过本机3D零件和操作进行增强,分析和查看结果。

创建从本机3D零件创建设计或从3D实体模型导入。通过导入3D实体模型或3D本机零件和操作来扩展,分析和查看结果。

软件功能:

LarClarity 3D Solver使用行业领先的并行化技术来确保网格划分和清扫可以在尽可能多的计算机,计算机配置和核心之间进行分区和并行化。求解程序所需的时间是可伸缩的,具体取决于计算机核心的数量。如果将计算机内核数量增加一倍,性能将几乎提高一倍。

LarClarity 3D Solver包含Clarity 3D布局和Clarity 3D Workbench GUI工具,可用于设计PCB,IC封装和IC上系统(SoIC)设计的关键互连。

清晰的3D布局

LarClarity™3D Layout专为S参数模型提取而设计,可用于IC封装和PCB设计的电源完整性(PI)和信号完整性(SI)分析。改进的自适应有限元网格(FEM)技术为复杂的3D结构提供了一致的精度。借助Clarity 3D Layout,您可以轻松导入Cadence PCB和ICP文件格式以及行业标准文件格式(如IPC2581)。

清晰度3D工作台

LarClarity™3D Workbench使您能够导入机械结构,例如电缆和连接器,并将它们与PCB合并,以便您可以对从板到连接器的关键3D结构进行建模和优化,并将其建模为一个结构。您可以轻松导入行业标准的机械文件格式,例如Clarity 3D Workbench中的STEP

安装步骤:

1.用户可以单击本网站提供的下载路径下载相应的程序安装包

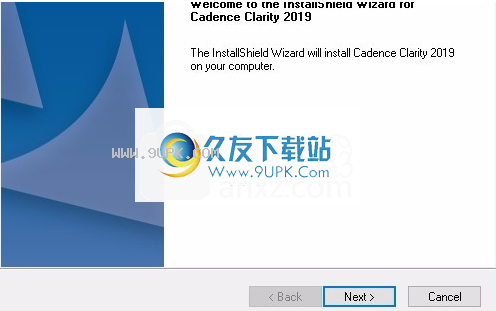

2,只需使用解压功能打开压缩包,双击主程序进行安装,弹出程序安装界面,单击许可进行安装

3,然后关闭许可证安装界面,直接×放

4.现在返回安装界面,然后单击以继续安装产品安装,等待程序数据加载

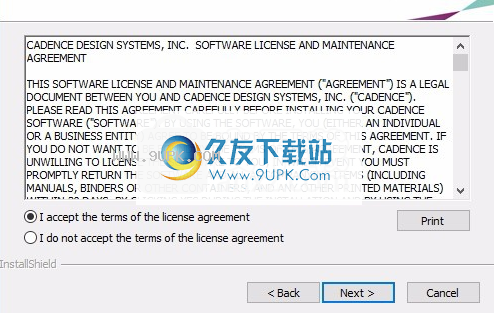

5.同意协议条款,然后继续安装应用程序,单击同意按钮

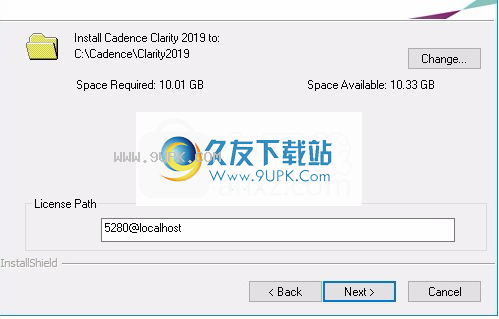

4.您可以单击浏览按钮,根据需要更改应用程序的安装路径。

5,弹出以下界面,用户可以直接用鼠标点击下一步按钮,可以根据需要安装不同的组件

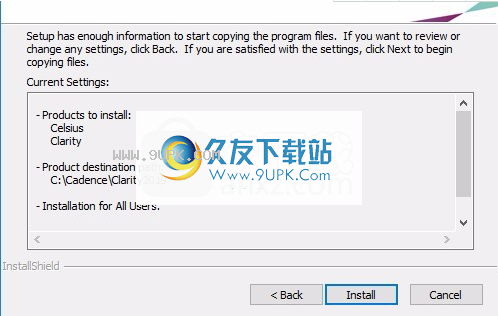

6.现在准备安装主程序,单击安装按钮开始安装。

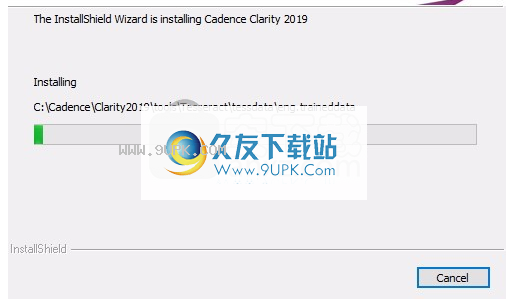

7.弹出应用程序安装进度栏加载界面,等待加载完成

8.根据提示单击“安装”,弹出程序安装完成界面,单击“完成”按钮。

使用说明:

1.区域分工

完成PCB布局后,设置电气规则,间距,物理规则和区域规则,将布线层划分为Partition区域,并设置Guideports。

每个人都要负责主要设计的一个领域。这时,团队成员的布线进度可以在主设计中看到。可以在主设计和子设计之间执行动态ECO输入和输出。

2.合作接线

每个PCB团队成员都要进行子模块设计调整,并按照主设计制定的规则完成每个子设计的布局,然后将ECO反馈给主设计。合并后,将进行最终调整。

优势团队设计优势

Allegro Team Design技术提供了一种多用户并行设计方法,可以加快产品上市时间并缩短设计时间。无论团队的地理距离如何,并行进行设计的多个工程师都可以访问同一数据库。工程师可以将设计分为几个部分或区域,并且设计团队的几个成员可以同时执行设计优化。

统一的数据库确保团队设计的正确性

减少设计周期

允许并发设计,指派具有专业知识的设计师来设计自己的专业领域,并最大程度地提高设计效率

智能ECO双向同步设计,及时跟踪团队成员进度,降低设计成本

随着电子技术的发展,PCB系统需要越来越多的功能,并且PCB的复杂性也在增加。系统规划和模块化将使设计更加容易,并且多人协作设计非常符合团队工程师的协作设计。同一块PCB的功能使不同的工程师可以设计自己擅长的电路,例如电源模块,RF模块,数字模块,接口模块等。

俗话说“人人都挑高火柴”,高效合理地划分电路板,多人协同设计可以多次提高项目设计进度的要求。使用本地电气规则,定义接口Gideports的对接位置,并允许多个人协作执行布局和布线工作,从而缩短设计时间并提高效率。

许多电子设计工程师依靠在面包板上构建电路来验证设计操作和功能。

尽管此技术是一种完全有效的概念证明方法,但它具有固有的局限性。

设计人员将花费很长时间来收集组件,将这些组件连接到试验板上,准备上电状态,然后手动测量结果。

仿真使用PSpice A / D和高级分析选项来仿真电路设计可以大大减少这些时间。

此外,电路调试伴随着无休止的组件更换和组合,使得大规模手动处理重复的时间和成本难以承受。

差异电子元件的生产差异将影响电路的功能和性能。

Ť这些生产差异通常反映在主要部件规格的公差范围内。测试电路所有组件的整个公差范围通常是不可能或不实际的。

组件的公差也可能会影响某些电路性能,因此可能会超出某些组件的使用限制。超过使用限制将导致组件损坏和电路功能故障。

manufacturers对于制造商来说要解决这些可能的问题的影响是昂贵的。

产品发布时没有进行公差分析,制造商不知道电路在批量生产期间将如何工作。

结果是一定比例的产品不能达到预期的效果。在许多情况下,产品测试是在包装和运输产品之前执行的。

此测试将筛选出有缺陷的产品,并且被筛选的产品可能会被修理,重新测试或报废。

许多制造商认为测试,返工和报废是业务运营的必要部分,但是合理的设计可以使制造商减少返工和报废。

完善的声音设计可以通过一些方法来实现。这些方法包括:考虑组件的公差并设计电路,以便组件可以使用其值范围内的任何值。

工程师可以通过紧缩所有组件的公差来使设计更坚固,但是紧缩公差意味着使用价格更高的组件。过度设计的设计公差将增加产品生产成本,并降低公司可实现的利润。

但是,在某些实际情况下,由于人为因素最终无法通过测试,因此一些有缺陷的产品被运送给客户。发生问题时,制造商需要安排退回已装运的有缺陷的产品,

同时,请技术人员对客户进行故障排除和维修,或者进行召回。现场故障是制造商必须处理的最昂贵的问题,并且可能导致潜在的安全隐患,伤害,诉讼,集体诉讼,定罪和罚款,更不用说严重损害公司的声誉了。

PSpice仿真工具为电路分析提供了一种行之有效,便捷的方法,以推断电气工程师的电路设计是否合理,从而大大提高了电路设计的效率。

借助这种强大的电路分析环境和分析功能,工程师可以确保满足要求的电路功能和公差没有问题。不必担心生产成本超过标准以及生产太多不合格产品。

这样可以提高产量,减少原型制作,减少实验时间并最终降低产品成本,从而增加潜在利润。

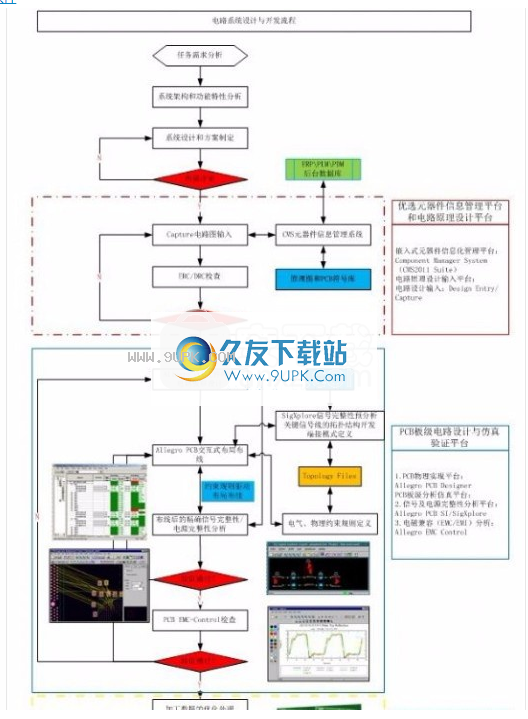

电路原理系统仿真与验证设计过

电路系统设计归因于设备,材料和工艺的发展。同时,为了减少原型设计并提高设计效率,可以提高产品可靠性。

目前,电路系统设计仿真和验证已成为电路设计工程师的桌面工具。国外一直对仿真平台的建设给予更多的关注,并在研发过程中对仿真提出了明确的要求。

尤其是随着硬件和软件水平的急剧提高,这为精确的仿真结果提供了便利。

同时,它也促进了仿真的普及。

由于中国项目研究和开发的紧迫性,国内建模能力也得到了极大的提高,一些国内电路系统设计单位也开始重视仿真平台的建设。

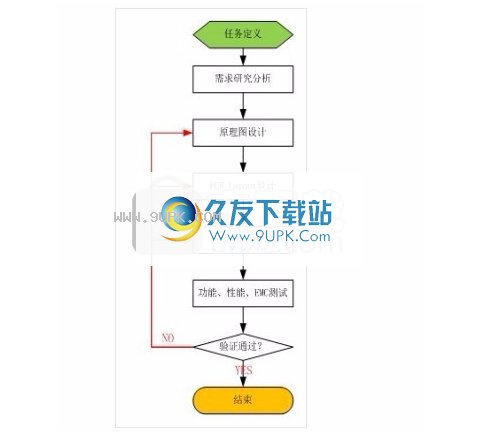

以下是传统设计方法和优化的仿真过程方法之间的设计过程比较:

图:传统设计流程图定义

1.传统的设计过程称为原型方法,这是一种问题补救方法:

没有提前

测试和控制节点,依靠设计者的经验;

才能在原型制作出来并进行调试之后,您可以知道设计是否成功;

如果有问题,则需要查找,定位和解决问题。接下来,一切都从头开始,并开始另一个周期

值得注意的是,测量,发现和定位由各种电路的操作引起的一些问题是一项艰巨的任务。

2.解决问题的时间和成本与产品开发阶段成正比。

Thermaltake处于产品开发的后期阶段。

越解决问题的手段越少;

解决问题的成本越高;

越需要的时间越长;

3传统的设计过程强调设计师的问题诊断技术和经验。致命的缺点是设计过程是不可控制的(包括产品质量,开发周期和设计成本)。

4.许多简单,重复的工作,这消耗了设计人员的有效时间。

5.标准化很难满足要求。

6.产品的可靠性和一致性很难保证。

7.使产品调试周期不可控,并直接影响产品的上市时间。

通过优化设计过程,建议使用产品设计+模拟闭环设计,这可以为工程师带来新的设计方法和经验积累,并快速建立和提高公司的设计研发能力。其次,它可以规范设计师的行为,并帮助公司建立和改善标准化的设计流程,从而帮助公司节省大量研发成本,进一步加快产品开发周期,同时确保产品的一致性和可靠性。

优势优化流程的优势:

1.专业分工

统一数据库建设的管理和维护,并通过限制设计人员的行为来帮助公司建立标准化的设计流程。

完成系统设计的预评估和分析。

电路原理级仿真和板级仿真的信号完整性/电源完整性/ EMC / EMI分析有助于提高产品“单次设计成功”的可能性。

2.加强设计阶段验证和“ IP”积累,并在设计的每个阶段设置可控点

建立符合标准的企业级图书馆管理系统(CMS-Components Manager System)。

加强系统级仿真验证。

加强开发和验证板级系统的关键信号规则。

在各级建立成功的“ IP”资源库。

3,企业新设计方法的好处

在产品设计的早期阶段减少资源浪费。

增强每个阶段设计正确性的可控性,并对可能的设计问题进行定性和定量分析。

将大量调试工作提前到设计阶段,从而增强了调试阶段的时间可控性。

缩了整个产品开发和调试周期,并节省了开发成本。

提产品的可靠性和一致性。

![CAD好帮手 1.0.9中文免安装版[图纸比较格式转换功能]](http://pic.9upk.com/soft/UploadPic/2013-7/20137187204368267.gif)