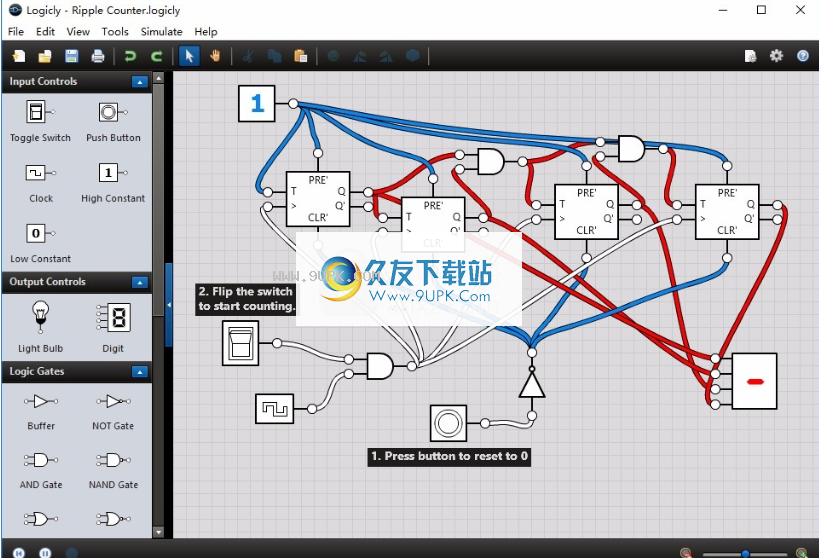

Logicly是一款非常好用的电路仿真模拟工具。行业必备的电路仿真模拟软件Logicly。该软件提供许多组件。使用鼠标单击时,可以将组件拖动到设计区域。您可以设置组件的名称,并调整组件的属性。添加多个电气组件后,可以在软件中设置连接方法,并直接在软件中选择电线连接。将各种电路组件连接到完整的电路中。要创建连接,请单击组件的输出引脚(圆形连接器,通常在右侧),然后将电线拖到兼容的未连接输入引脚上。该引脚将以蓝色突出显示。输入引脚只能连接到一个输出引脚,一个输出引脚可以连接到多个输入引脚。然后,您可以在软件中测试电路是否可以正常运行,并启动仿真操作功能。用软件测试电路!

软件功能:

1.运行模拟

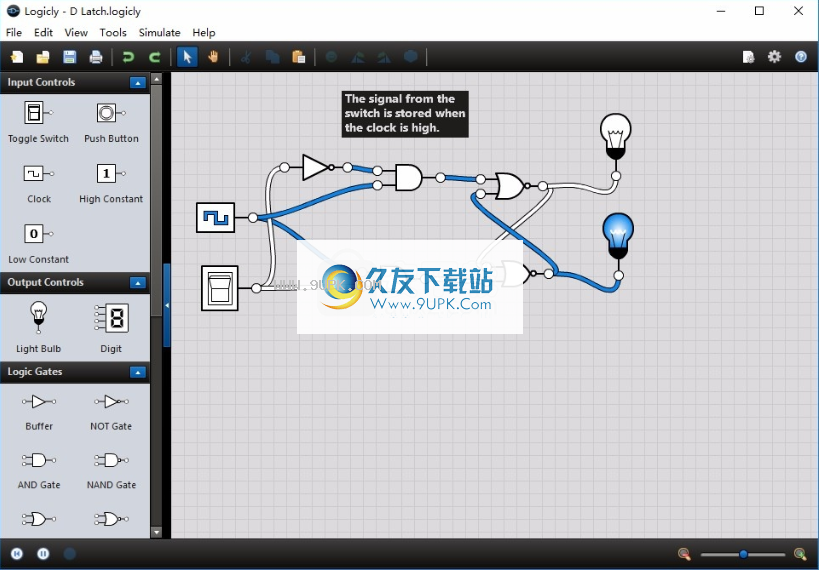

创建或打开文档时,Logic会自动启动模拟。信号将立即在连接的组件之间传播,如果您的电路包含一个或多个时钟,它们将开始振荡。

2.逻辑与逻辑色彩

信号由逻辑中的颜色表示。当引脚更改状态或创建或删除连接时,连接对象和某些对象本身的导线可能会在编辑面上更改颜色。

蓝色表示信号处于高状态(真)。

白色表示信号处于低电平状态(错误)。

灰色表示信号处于高阻抗状态(hi-Z)。

红色表示信号处于错误状态。

3.定制集成电路

定制集成电路使您可以将文档的复杂子集打包到单个可重用组件中,类似于触发器。

4.设计电路

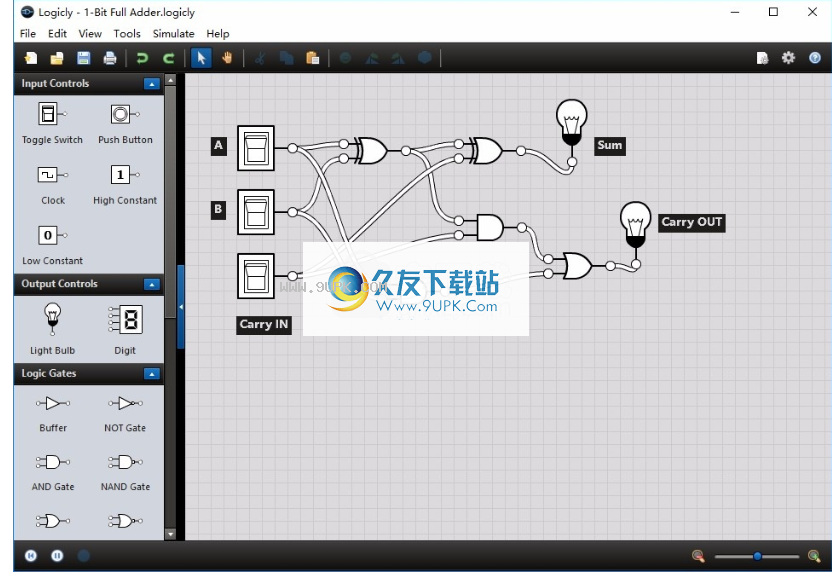

从Logic的角度来看,您可以在编辑面上拖放组件,并使用鼠标轻松地对其进行操作。

使用组件

要将组件添加到文档中,请将其从窗口左侧的组件选择器拖动到右侧的编辑表面。释放鼠标左键,然后将其放置在编辑面上的任何位置。

要选择文档中的单个组件,请用鼠标单击它。它将以蓝色突出显示,表明已被选中。

5.零件和电线

更改对象在编辑表面上的外观和行为。

如果需要,可以在逻辑门符号的不同标准之间更改符号样式。 ANSI / IEEE标准提供独特的形状,而IEC标准使用矩形。

安装方式:

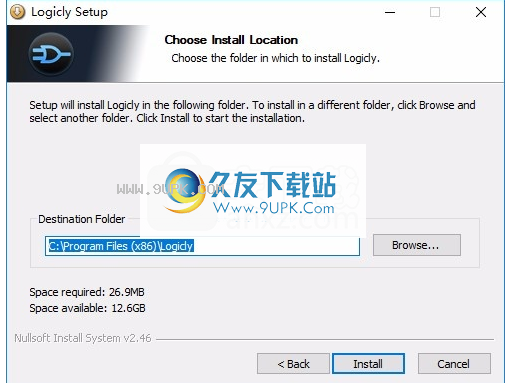

1.打开Logicly-1.7.6.exe软件并直接安装,然后单击下一步

2.软件的安装地址为C:\ Program Files(x86)\ Logicly

3.提示软件安装结束的界面,单击“完成”以结束安装。

官方教程:

示例:创建自定义的半加法器

为了更好地演示其工作原理,以下部分将指导您为半加法器创建定制集成电路。这是一个半加法器的现场演示:

首先在Logic中重新创建以上图表。拨动开关组件将成为输入连接器中的定制集成电路,灯泡组件将成为输出连接器。

选择顶部的拨动开关组件。

在属性窗口中,输入“导出名称”输入。导出名称值将显示在您的自定义IC上,输入或输出连接器旁边。如果文本很长,则可能会自动将其缩短并加上省略号。

选择底部的切换开关组件,然后在属性窗口的“导出名称”输入框中键入B。

选择顶部灯泡组件,然后在属性窗口中输入“出口名称”输入框(代表“ sum”)。

选择底部的灯泡组件,然后C在属性窗口的“导出名称”输入框中输入(“携带”)。

如果您的文档包含超过一半的加法器,请从“编辑”菜单中选择“全选”,或在整个半加法器电路周围拖动选择矩形。

从“编辑”菜单中,选择“创建集成电路...”。

现在,您应该看到“创建集成电路”窗口。当您的选择不包括至少一个拨动开关和至少一个灯泡时,将显示一条错误消息。同样,如果未在一个或多个拨动开关或灯泡上设置导出名称,则将显示错误。

在“全名”输入框中,输入定制集成电路的完整和详细名称。该文本将出现在“逻辑”主窗口左侧的组件列表上显示的标签中。对于此示例,我们应输入Half Adder。

在“符号标签”输入框中,可以输入一些简短的标签文本,以显示在电路符号的中心。该字段是可选的,但为清楚起见建议使用。同上,我们将输入Half Adder。如您在上面的屏幕截图中所见,您可以选择在标签文本中包含换行符。我们还可以考虑使用HA之类的缩写来减少编辑器中的空间。

最后,您可以更改每个输入和输出连接器的位置。默认情况下,所有输入都出现在左侧,所有输出都出现在右侧,类似于逻辑门。但是,您可以按任意顺序将任何连接器拖到符号的顶部,右侧,底部或左侧。对于半加法器,我们将所有输入保留在左侧,将输出保留在右侧,但是您可以根据需要将它们拖动到不同的位置。

完成所有操作后,单击“创建IC”按钮。

新的定制集成电路将出现在“逻辑”主窗口左侧的组件列表中。您会在列表底部找到一个名为“自定义”的新类别。要使用新的Half Adder电路,只需将其拖到编辑器中,然后像其他任何组件一样将其连接到输入和输出即可。

删除定制集成电路

在Logicly主窗口左侧的组件列表中找到定制集成电路。它应显示在“自定义”类别中。右键单击定制电路图标,然后选择删除IC。

如果当前文档中正在使用要删除的定制组件,或者设计中包含另一个定制组件,则会显示一条错误消息,指出无法删除定制电路。

查看定制集成电路的内容

创建定制集成电路后,您可以查看其设计,但不能对其进行编辑。在“自定义”类别下的“组件”列表中找到自定义集成电路。右键单击并从上下文菜单中选择“查看IC ...”。父文档将被暂时隐藏,并且将显示您的自定义集成电路。在此视图中,可以平移和缩放以浏览电路,并且所有组件均正常工作。这是一个与主文档完全隔离的独立模拟,因此,如果您选择与组件交互,则不会有任何后果。完成后,单击Logicly主窗口左上角的“关闭”按钮以返回到父文档。

或者,要查看定制集成电路的内容,可以在编辑界面上双击其实例。

由于自定义集成电路创建后无法编辑,因此在查看电路内容时可以使用“复制到剪贴板”按钮。您可以使用它将内容粘贴回父文档中,以对其进行编辑并创建新的自定义集成电路。

分享定制集成电路

在多个文件之间

与另一文档共享定制集成电路有两种方法。最简单的方法是在第一个文档的编辑表面上选择任何集成电路,将其复制到剪贴板,然后将其粘贴到第二个文档中。定制集成电路将自动添加到组件列表中,您可以在第二个文档中的任何位置重用它,就像在此处最初创建时一样。

如果要在单独的外部文件中管理一组集成电路,则可以将组件列表导出到集成电路库文件。

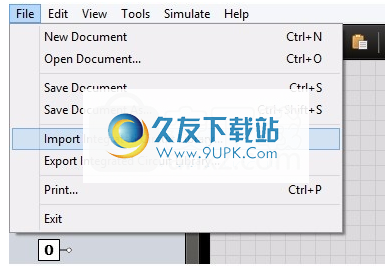

打开文件菜单,然后选择导出IC库...。将打开一个保存文件对话框。选择位置时,包含当前文档的所有集成电路的逻辑库文件将保存到您的计算机中。

从上面的屏幕快照中可以看到,您还可以从“文件”菜单中选择“导入IC库...”。从计算机中选择逻辑库文件后,该文件中包含的所有自定义集成电路都将添加到当前文档中。如果当前文档中已经存在库中的任何定制集成电路,则Logic将不会创建重复的集成电路。您创建的每个新的定制集成电路都有一个唯一的ID,该ID在添加它的每个文档中都以相同的方式对其进行标识。

使用连接

通过使用“电线”连接组件,信号在电路周围传递。

要创建连接,请单击组件的输出引脚(圆形连接器,通常在右侧),然后将导线拖到未连接的输入引脚上。兼容的引脚将以蓝色突出显示。输入引脚只能连接到单个输出引脚。一个输出引脚可以连接到许多输入引脚。

要删除连接,请单击导线以将其选中,然后单击上方工具栏中的“删除”按钮。或者,您可以右键单击并从上下文菜单中选择“删除连接”。

提示:将鼠标悬停在电线上时,它将重新排列到顶部。如果您的电路特别复杂,这对于确定连接单根电线的位置将非常有帮助。

要向连接添加点,请单击并拖动导线。将添加一个点。或者,您可以右键单击导线,然后从上下文菜单中选择“添加点”。

提示:该点将与同一条线上的其他点对齐到相同的垂直和水平位置。使用此功能可以创建完美的直线和90度角。

要从连接中删除一个点,请右键单击该点,然后选择“删除点”。

对象类型

可以将以下对象添加到电路中。

拨动开关输出高(真)或低(假)信号(从不输出高阻抗(Hi-Z)或错误)。您可以通过单击开关来切换状态。

默认情况下,按钮输出一个低(假)信号,或在按下时输出一个高(真)信号。

时钟以在设置的时间段内在高(真)和低(假)信号之间振荡。其状态通过仿真自动更改。

恒定的装甲高度始终会输出高(真)信号。

低数始终输出低(假)信号。

一个灯泡用颜色显示输出引脚的当前状态。

一个4位显示的十六进制数字(0x0-0xF)由四个输入组成。

缓冲区只是传播它接收的信号。在现实世界中,如果缓冲器失去强度,它将增强电信号。在Logic的仿真中,缓冲区可用于影响传播时间。

“非”门会将高(真)信号变为低(假)信号,或将低信号变为高信号。

AND门将对其输入信号执行布尔AND功能。

Afgate将对其输入的信号执行布尔NAND功能。

或门将执行其输入信号的布尔或功能。

或非门将对其输入信号执行布尔或非运算。

XOR门将对其输入的信号执行布尔XOR功能。

X的XNOR门将对输入处的信号执行布尔XNOR功能。

如果三态使能输入为高(真),则三态传播其接收的信号。如果使能输入处于低(假)状态,它将输出高阻抗(hi-Z)信号。

SR触发器是最简单的触发器类型。主机和从机在时钟输入的负沿触发。

d触发器在时钟的上升沿存储数据。它具有用于预设和清除的异步输入,并且当输入信号为高(真)时,这些输入无效。此实现基于IC 7474。

JK触发器是SR触发器的改进,因为它被设计为在置位和复位输入都为高电平(true)时避免竞争情况。就像上面的D型触发器一样,

JK触发器由一个上升沿触发,它具有用于预置和清除的异步输入,当输入信号为高(真)时,它们无效。

当输入T时,T触发器将其输出切换为高电平(真)。像上面的D和JK触发器一样,该T触发器由上升沿触发。它具有用于预置和清除的异步输入。当输入信号为高(真)时,它们无效。

总线可以将多个连接合并为一个连接。它通常与三态缓冲器组合,通过忽略任何高阻抗(hi-Z)信号,仅从其各种输入输出一个信号。如果总线同时接收到高(真)和低(假)信号,它将输出错误信号。

如果上拉输入为高阻抗(hi-Z),则上拉将输出高(真)信号。所有其他输入信号将被传播而不会发生变化。

如果下拉输入为高阻抗(hi-Z),则下拉输出为低(false)。所有其他输入信号将被传播而不会发生变化。

使用说明:

1.打开逻辑以提示协议内容,并在软件界面中接受协议

2.提示试用界面,可以选择试用30天

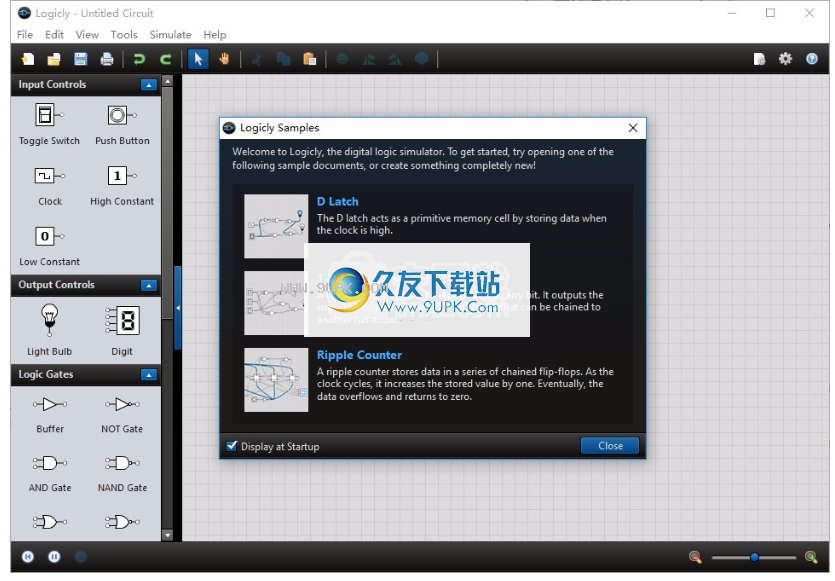

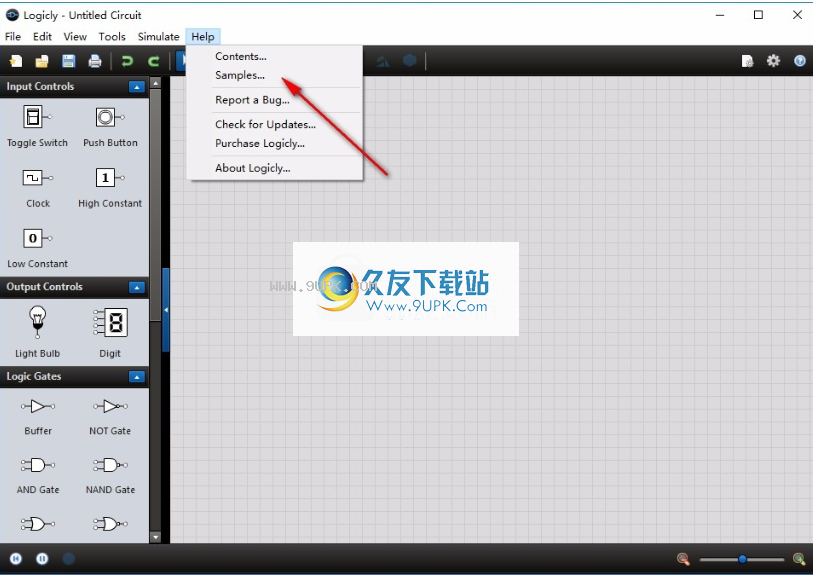

3.欢迎使用Logicly。首先,尝试打开下面的示例文档之一,或创建一个全新的文档!

4.D锁存器,当时钟为高时,D锁存器通过存储数据而充当原始存储单元。

5.1位全加器,一个全加器将进位加到两个1位输入。输出总和。第二个输出位是一个进位位,可以链接到另一个完整的加法器。

6.纹波计数器,纹波计数器将数据存储在一系列链接的触发器中。随着时钟周期,它将存储的值增加一。最终,数据溢出并返回零。

7.您可以查看帮助内容在软件中了解Logic如何设计电路

软件特色:

可用组件

逻辑上提供各种逻辑门,触发器和其他组件,用于设计逻辑电路。

对象类别

人们可以根据其功能将添加到电路中的对象分为几个不同的类别。

输入控件可以将高(真)或低(假)信号传递到电路。某些功能(例如Toggle Switch)可以通过用户输入来更改状态。其他时钟(例如Clock)可能会根据时间或其他由模拟控制的因素来更改状态。

您可以将输出控件连接到输出引脚以显示其当前状态。

逻辑门在其输入引脚的状态上执行布尔逻辑功能。

触发器可以存储一位数据。

其他控件包括不适合其他类别的各种对象。

将来的Logic版本中可能会添加更多类别。

![CapacityCalc 4.31a免安装版[raid组容量计算器]](http://pic.9upk.com/soft/UploadPic/2013-10/20131019391774536.gif)

![RapidCRC Unicode[CRC检验软件] 0.3.17 免安装版版](http://pic.9upk.com/soft/UploadPic/2015-10/201510268284731340.gif)